eMMC识别流程简介

之前文章介绍了 Boot mode,eMMC操作模式-Boot mode,这次介绍 Device identification mode和 Data transfer mode,即 Normal mode。

Normal mode涉及到的速度模式主要包括:High-speed、HS200和 HS400。

Device identification mode

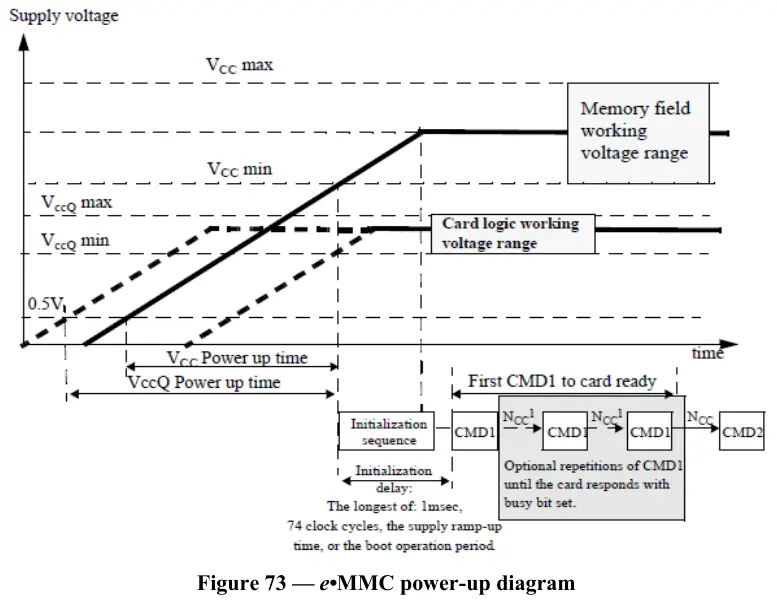

1、Power-up,向器件 VCC(3.3V)和 VCCQ(3.3V / 1.8V)提供电源。设置时钟最大到 400KHz,host等待 74 clock cycles或者是电源电压上升至 3.3V,最大等待 1ms;

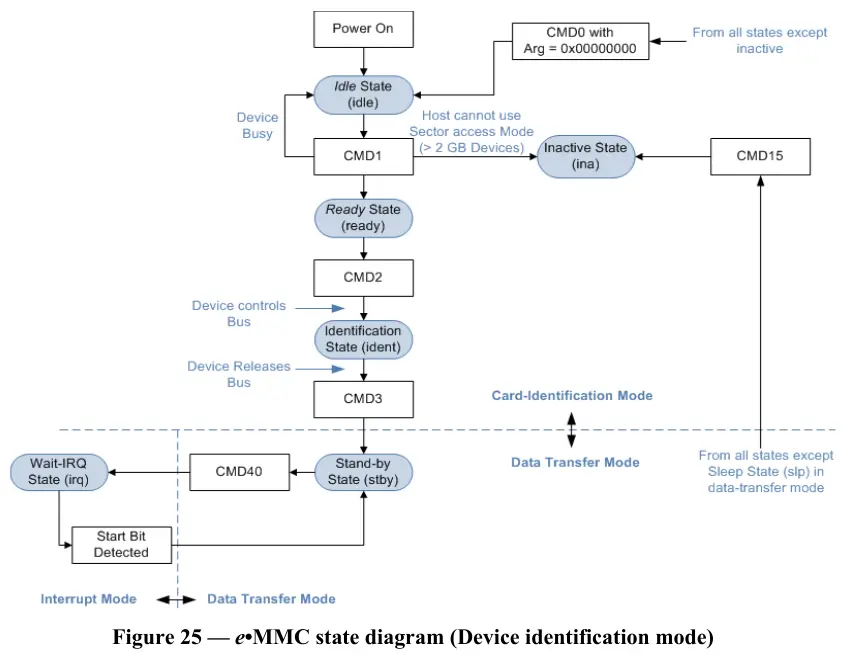

2、进入 Idle State,Power on后有 4种情况进入 Idle State:a. Boot mode完成后,b. Pre-boot state下 CMD拉低的时间少于 74 clock cycle或 Boot sequence失败,c. EXT_CSD[179] BOOT_PARTITION_ENABLE = 0,d. host发送 GO_PRE_IDLE_STATE(CMD0 with 0xF0F0F0F0);

3、访问模式确认,CMD1,host发送 CMD1(SEND_OP_COND),参数为 OCR寄存器,device并不需要理会里面的电压相关值,bit [23:7]。host会不断的发送 CMD1,直到 device完成初始化,容量小于或等于 2GB的 device会返回 R3 = 0x80FF8080,容量大于 2GB的 device返回 R3 = 0xC0FF8080,并且 device将会进入 Ready State;

循环的最后一次交互是有意义的,用于双方确认访问模式 bit [30:29] Access Mode,host不支持 Sector access Mode而 device只能使用该模式,则 device进入 Inactive State;

4、获取 CID,CMD2,host发送 CMD2(ALL_SEND_CID)获取 device的 CID,device进入Identification State;

5、分配 RCA,CMD3,host发送 CMD3(SET_RELATIVE_ADDR)给 device分配一个 RCA,device进入 Standy-by State,kernel一般分配是从 0x1开始的。

完成 Device identification mode后,device处于 Backward Compatible,即 DS速度模式。

Data transfer mode

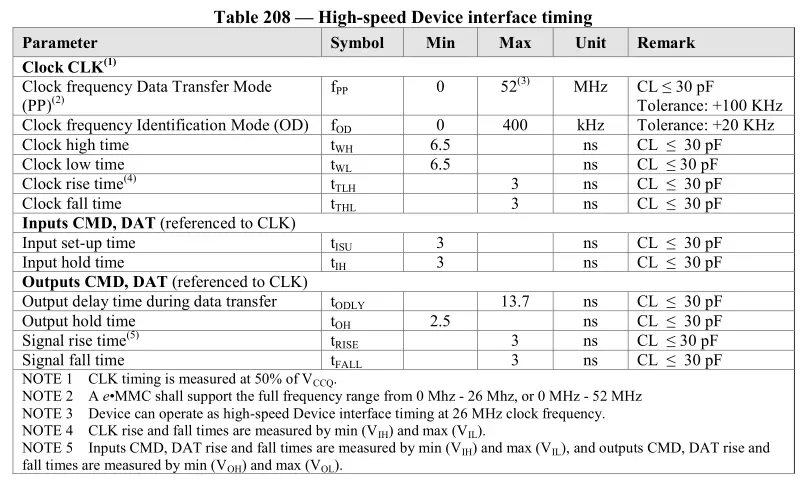

1、读取 CSD寄存器,CMD9,host不知道 device的 CSD寄存器值前,fpp(Clock frequency Data Transfer Mode,详见 Table 208,下图)应该要小于等于 fod(400KHz),host 发送 CMD9(SEND_CSD)获取 CSD寄存器,根据返回的信息对 host参数进行调整。例如,通过 TRAN_SPEED确定 device支持的最大时钟频率 fpp,CCC确定是否支持 CMD6(SWITCH)和 CMD8(SEND_EXT_CSD);

High-speed识别流程

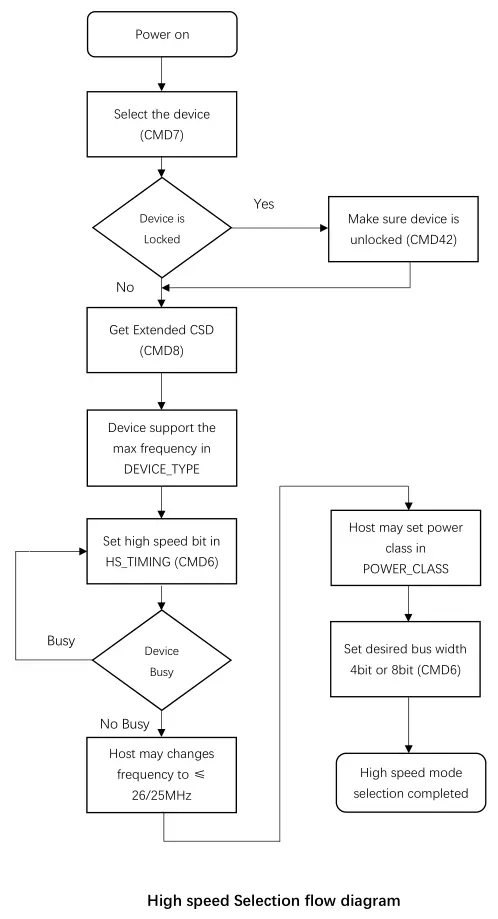

2、发送选卡命令,CMD7,host发送 CMD7,device进入 Transfer State,如果 device返回了 R1b响应,bit25 DEVICE_IS_LOCKED = 1,则 device已经锁定,需要在下一步操作前发送 CMD42解锁 device;

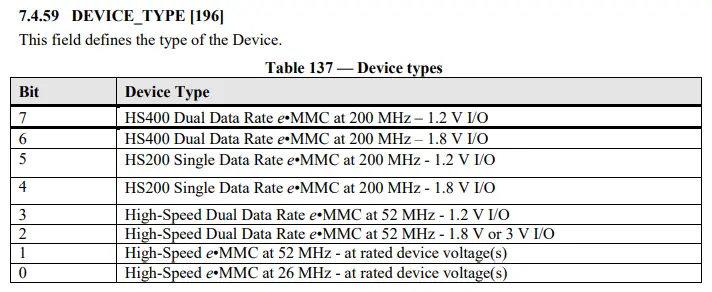

3、获取 EXT_CSD寄存器,CMD8,host发送 CMD8(SEND_EXT_CSD)获取 EXT_CSD寄存器,根据 EXT_CSD[196] DEVICE_TYPE,确认 device在 HS模式下的最高时钟频率;

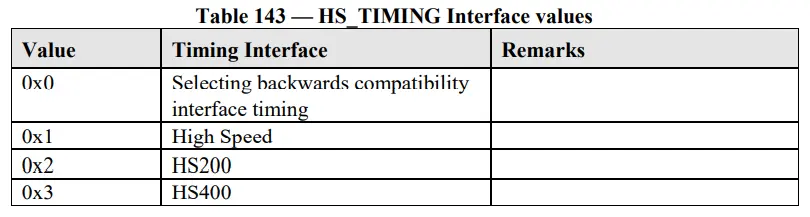

4、切换到 high speed模式,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[185] HS_TIMING的值设置为 0x1,device返回 R1b响应,host需要等待 BUSY signal(DAT0为低)解除,device从 BUSY恢复后,速度模式已经为 high speed(一定不能用 CMD13确认 device状态,uboot 2020掉过的坑);

5、切换时钟频率,host将自身的时钟频率切换到最大不超过 26/52MHz/TRAN_SPEED;

6、设置电源等级,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[187] POWER_CLASS的值设置为 host能为 device提供的最大能力值;

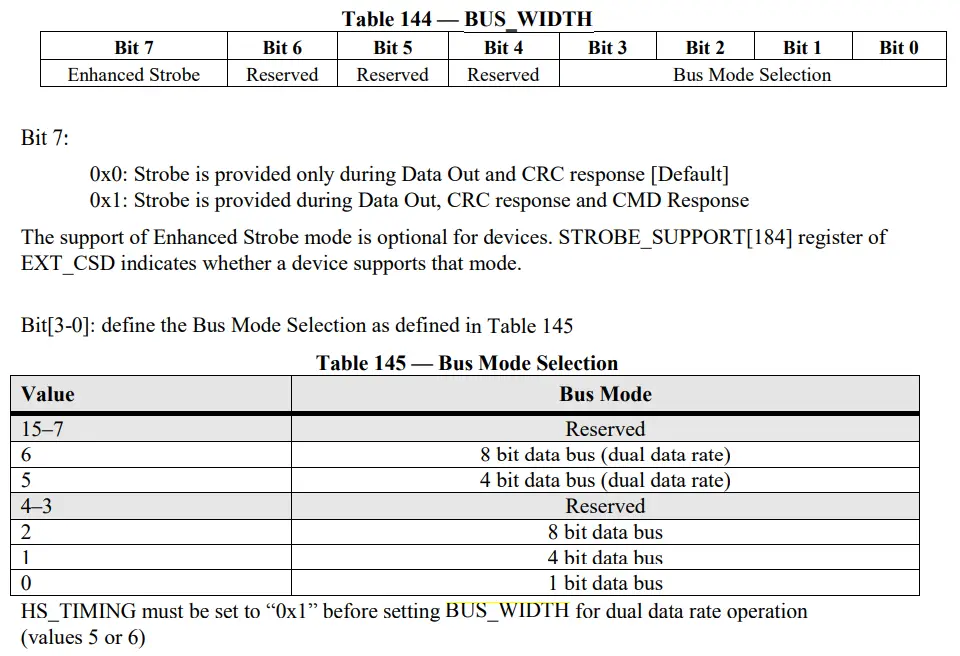

7、切换总线宽度,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[183] BUS_WIDTH的 bit [3:0]值设置所需的宽度,0x1为 4-bit,0x2为 8-bit。

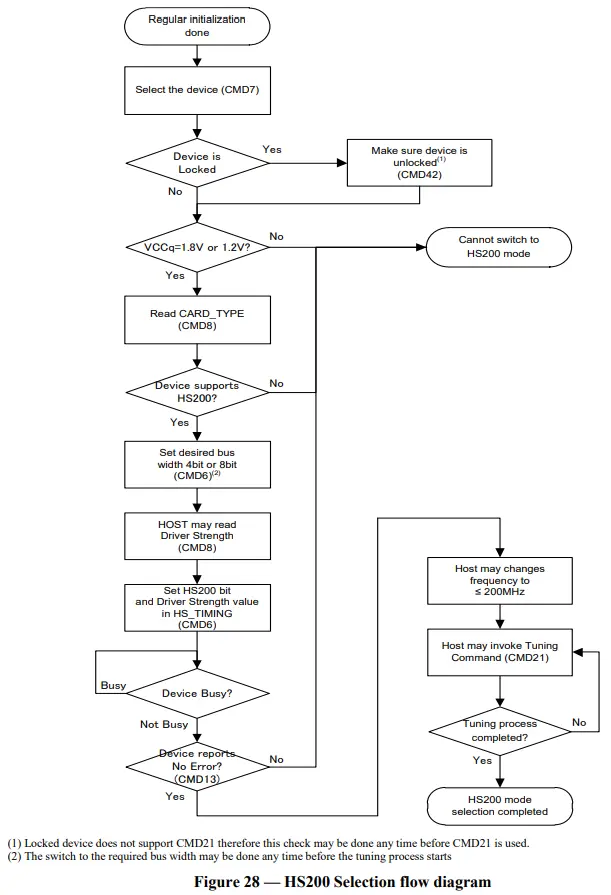

HS200识别流程

8、发送选卡命令,CMD7,host发送 CMD7,device进入 Transfer State,如果 device返回了 R1b响应,bit25 DEVICE_IS_LOCKED = 1,则 device已经锁定,需要在下一步操作前发送 CMD42解锁 device;

9、host IO电压确认,HS200 IO(VCCQ)只支持 1.8V/1.2V电压,host需要能提供相关电压;

10、获取 EXT_CSD寄存器,CMD8,host发送 CMD8(SEND_EXT_CSD)获取 EXT_CSD寄存器,根据 EXT_CSD[196] DEVICE_TYPE,确认 device是否支持 HS200和 IO电压;

11、切换总线宽度,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[183] BUS_WIDTH的 bit [3:0]值设置所需的宽度,0x1为 4-bit,0x2为 8-bit。

12、读取设备支持的驱动能力,查询 EXT_CSD[197] DRIVER_STRENGTH,获得 device支持的驱动能力;

13、切换到 HS200模式,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[185] HS_TIMING的 bit[3:0]设置为 0x2,bit[7:4] Driver Strength根据实际情况确定是否修改。device返回 R1b响应,host需要等待 BUSY signal(DAT0为低)解除;

14、查询状态,CMD13,host发送 CMD13(SEND_STATUS),device返回 R1响应,host确认 device已经处于 Transfer State且无错误状态,则表示速度模式成功切为 HS200;

15、切换时钟频率,host将自身的时钟频率切换到最大不超过 200MHz;

16、tuning of sampling point,CMD21,采样点优化,host将不同的采样相位设置给数字逻辑并发送 CMD21,从而确认最佳的采样相位,host可以在 CMD21失败的情况下发送 CMD12去停止该笔传输,再发送下一个采样点的 CMD21;

17、到此 HS200的识别流程就走完了。

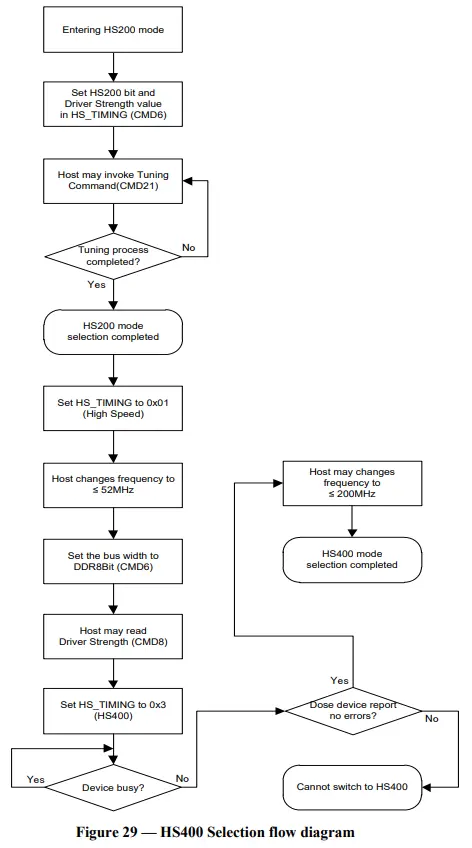

HS400识别流程

18、HS400是在 HS200完成的基础上进行的,HS400 IO只支持 1.8V/1.2V电压,总线宽度只支持 DDR 8bit;

19、获取 EXT_CSD寄存器,CMD8,host发送 CMD8(SEND_EXT_CSD)获取 EXT_CSD寄存器,根据 EXT_CSD[196] DEVICE_TYPE,确认 device是否支持 HS400和 IO电压,这步在 linux中可能是在步骤 10阶段完成;

20、切换到 high speed模式,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[185] HS_TIMING的值设置为 0x1;

21、切换时钟频率,切换时钟频率到小于或等于 52MHz;

22、切换总线宽度,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[183] BUS_WIDTH的 bit [3:0]值设置为 0x6,DDR 8-bit;

23、读取设备支持的驱动能力,查询 EXT_CSD[197] DRIVER_STRENGTH,获得 device支持的驱动能力;

24、切换到 HS400模式,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[185] HS_TIMING的 bit[3:0]设置为 0x3,bit[7:4] Driver Strength根据实际情况确定是否修改,device返回 R1b响应,host需要等待 BUSY signal(DAT0为低)解除;

25、查询状态,CMD13,host发送 CMD13(SEND_STATUS),device返回 R1响应,host确认 device已经处于 Transfer State且无错误状态,则表示速度模式成功切为 HS400;

26、切换时钟频率,host将自身的时钟频率切换到最大不超过 200MHz;

27、因为采样相位使用的是 HS200的,所以 HS400就不用 tuning,到此 HS400的识别流程就走完了。

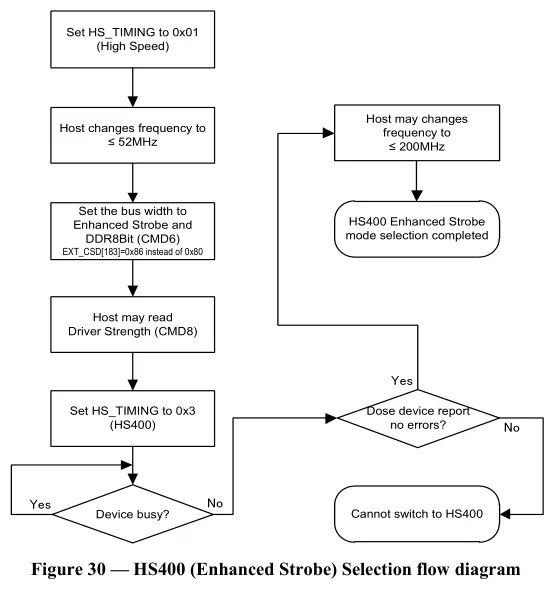

HS400ES识别流程

28、HS400ES即 HS400 Enhanced Strobe,HS400模式,引入了 Data Strobe线,使得数字逻辑在 Data Out、CRC response上不依赖 tuning流程就可以确认最佳采样相位,但 CMD Response没有这个机制,Enhanced Strobe就是用来弥补这个事情的。

29、发送选卡命令,CMD7,上接步骤 “1、读取 CSD寄存器”,host发送 CMD7,device进入 Transfer State,如果 device返回了 R1b响应,bit25 DEVICE_IS_LOCKED = 1,则 device已经锁定,需要在下一步操作前发送 CMD42解锁 device;

30、获取 EXT_CSD寄存器,CMD8,host发送 CMD8(SEND_EXT_CSD)获取 EXT_CSD寄存器,根据 EXT_CSD[196] DEVICE_TYPE,确认 device是否支持 HS400和对应的 IO工作电压;

31、确认是否支持 Enhanced Strobe,根据 EXT_CSD[184] STROBE_SUPPORT,确认 device是否 Enhanced Strobe,支持为 0x1;

32、切换到 high speed模式,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[185] HS_TIMING的值设置为 0x1;

33、切换时钟频率,切换时钟频率到小于或等于 52MHz;

34、切换总线宽度,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[183] BUS_WIDTH的 bit [7]值设置为 0x1,bit [3:0]值设置为 0x6,使能 Enhanced Strobe和 DDR 8-bit;

35、读取设备支持的驱动能力,查询 EXT_CSD[197] DRIVER_STRENGTH,获得 device支持的驱动能力;

36、切换到 HS400模式,CMD6,host发送 CMD6(SWITCH)将 EXT_CSD[185] HS_TIMING的 bit[3:0]设置为 0x3,bit[7:4] Driver Strength根据实际情况确定是否修改,device返回 R1b响应,host需要等待 BUSY signal(DAT0为低)解除;

37、切换时钟频率,host将自身的时钟频率切换到最大不超过 200MHz;

38、HS400 Enhanced Strobe的识别流程也介绍了。

详细的流程详见 6.6.2 High-speed modes selection和 A.6 High-speed e•MMC bus functions,以及 Linux和 u-boot的代码,毕竟有很多兼容性的点是协议不会描述的。